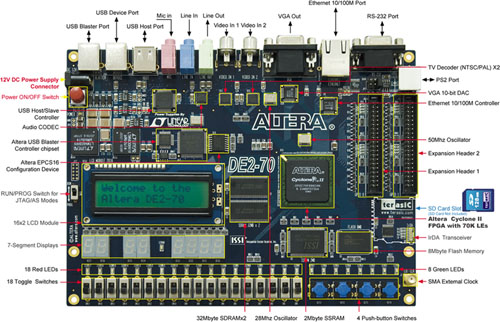

NIOS 및 FPGA, Verilog, VHDL을 공부하기 위해 구매한 DE-70 보드이다. Altera Cyclone2 EP2C70 기반이다. 제품의 모습은 아래와 같다. 클릭해서 보면 잘보인다. 자세한 사양은 아래와 같다. The DE2-70 board has many features that allow the user to implement a wide range of designed circuits, from simple circuits to various multimedia projects. USB Blaster (on board) for programming and user API control; both JTAG and Active Serial (AS) programming modes are..